Image processing Systems

Traana has done significant work in the domain of Image Processing for Defence Applications; both FPGA based sophisticated hardware and as well as Software based Algorithms.

Our team has been involved in design and development of advanced image processing applications and algorithms, based on Realtime stand-alone FPGA based embedded systems, for Image Acquisition, Image Compression, Storage and Retrieval, Target Detection and Classification (i.e., Segmentation, Representation, Description and Classification). In addition, we have developed CUDA (Compute Unified Device Architecture) based Image Enhancement and Dehazing Algorithms. The systems and algorithms thus designed work over standard interfaces such as Camlink.

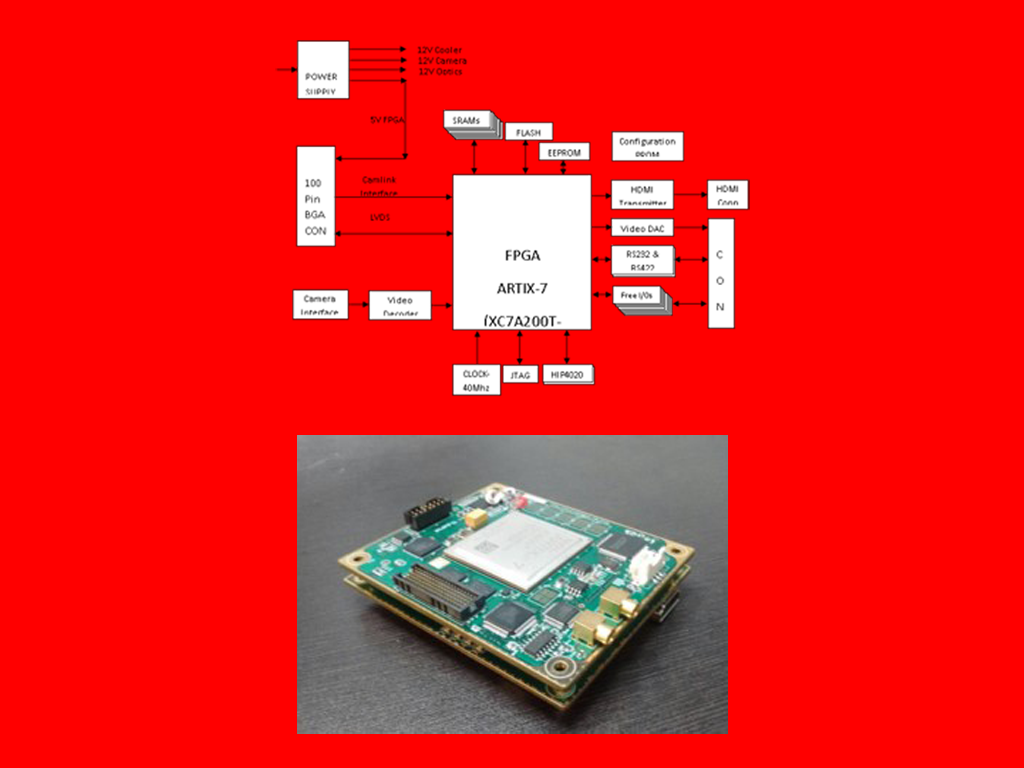

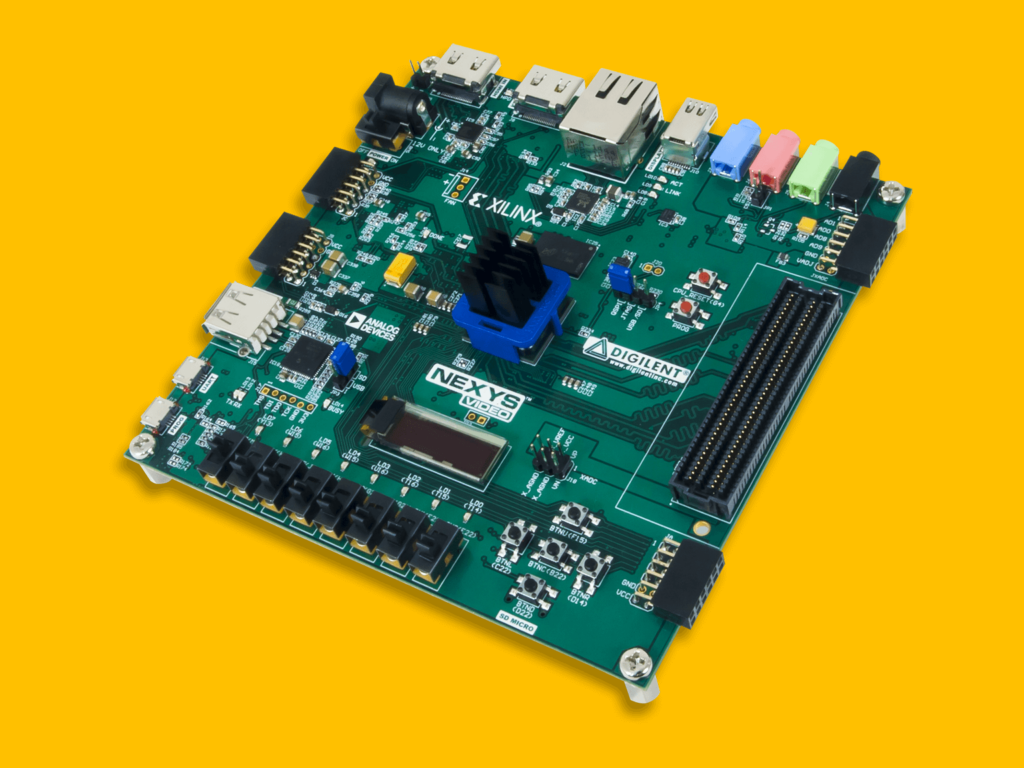

HD Detector Based Surveillance System

based on ARTIX-7 FPGA

FPGA: ARTIX-7 from Xilinx

MEMORY:

Asynchronous SRAM

FLASH

SPI FLASH MEMORY

PROM

VIDEO INTERFACES:

Video Input:

Camera Link Receiver

It takes digital video input from sensor over the

LVDS link and converts it into 28-bit digital signals

Video Output:

RGB video output

HDMI Transmitter

Video Compression and Storage Module

FPGA

Artix 7 FPGA from Xilinx

DMSoC

Digital Media System-on-Chip (DMSoC) from Averlogic

(AL582C) for H.264 video compression

Ethernet

10/100 Mbps.

Memory

32 GB NAND Flash for video and snapshot storage/

retrieval

1 Gb DDR2 RAM

Video capturing

PaI-B/XGA (monochrome and colour)

Digital video BT.656 standard

Storage

Video and snapshot storage at full format and frame rate on the onboard NAND Flash storage on user command

Control and Communication

RS232 Serial link

Output

Stream H.264 encoded video to Ethernet

Retrieval/transfer of stored videos & images from 32GB

NAND Flash via USB

Analog Video output playback

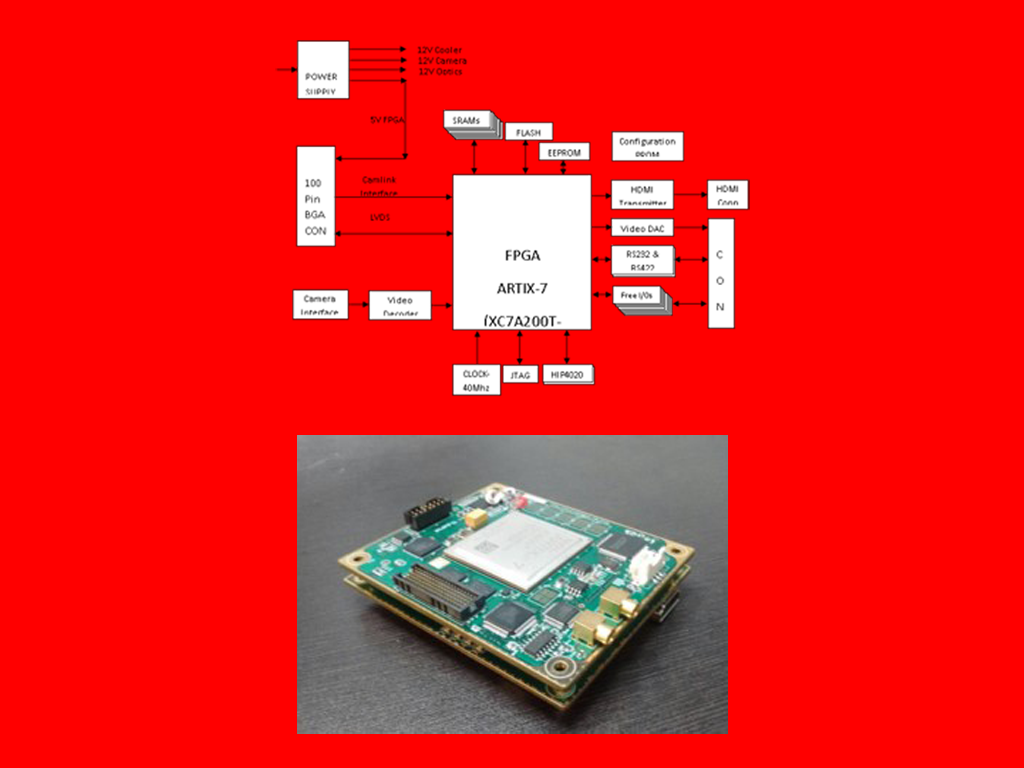

Target Detection and Classification

Module

Sub Modules

Backplane Card (BPC)

Interface Card (IFC)

Target Detection Card (TDC)

Important features

Scalable architecture

Input Voltage: 12V @ 10A with over voltage and reverse

polarity protection

Real time frame grabbing at 25 frames per second over

resolution of 1024 x 1024 pixels

194 – 512 x 512 point FFTs per second

FPGAs:

Artix 7-200T FPGA from Xilinx (5Nos.)

Artix 7-75T FPGA from Xilinx (1 No.)

SoC: Zynq 7020 SoC from Xilinx

Memory

64 GB NAND Flash for video storage/ retrieval

1 Gb DDR2 RAM

SRAMs

2 GB Parallel Flash

Video input

PAL/NTSC CCIR-B composite video via MCX connector

Camlink video via MDR 26 connector

Video Output

Composite video output via MCX connector

Camlink video output via MDR 26 connector

HDMI video output

Control and Communication

Gigabit Ethernet

USB 2.0 host with 2 port USB hub

USB-UART on each board for debugging

GPU based Image Processing Algorithms

Development and implementation of GPU based Image

Processing Algorithms for images and videos using

CUDA framework.

Platform:

Nvidia GE GTX-980

CUDA framework 6.5

Algorithms:

CLAHE (Contrast Limited Adaptive Histogram

Equalization) for Contrast Enhancement

De-hazing for foggy images

Use Cases:

Still images and Videos

Minimum frame rate of 20 fps for videos

Image processing Systems

Traana has done significant work in the domain of Image Processing for Defence Applications; both FPGA based sophisticated hardware and as well as Software based Algorithms.

Our team has been involved in design and development of advanced image processing applications and algorithms, based on Realtime stand-alone FPGA based embedded systems, for Image Acquisition, Image Compression, Storage and Retrieval, Target Detection and Classification (i.e., Segmentation, Representation, Description and Classification). In addition, we have developed CUDA (Compute Unified Device Architecture) based Image Enhancement and Dehazing Algorithms. The systems and algorithms thus designed work over standard interfaces such as Camlink.

HD Detector Based Surveillance System

based on ARTIX-7 FPGA

FPGA: ARTIX-7 from Xilinx

MEMORY:

Asynchronous SRAM

FLASH

SPI FLASH MEMORY

PROM

VIDEO INTERFACES:

Video Input:

Camera Link Receiver

It takes digital video input from sensor over the

LVDS link and converts it into 28-bit digital signals

Video Output:

RGB video output

HDMI Transmitter

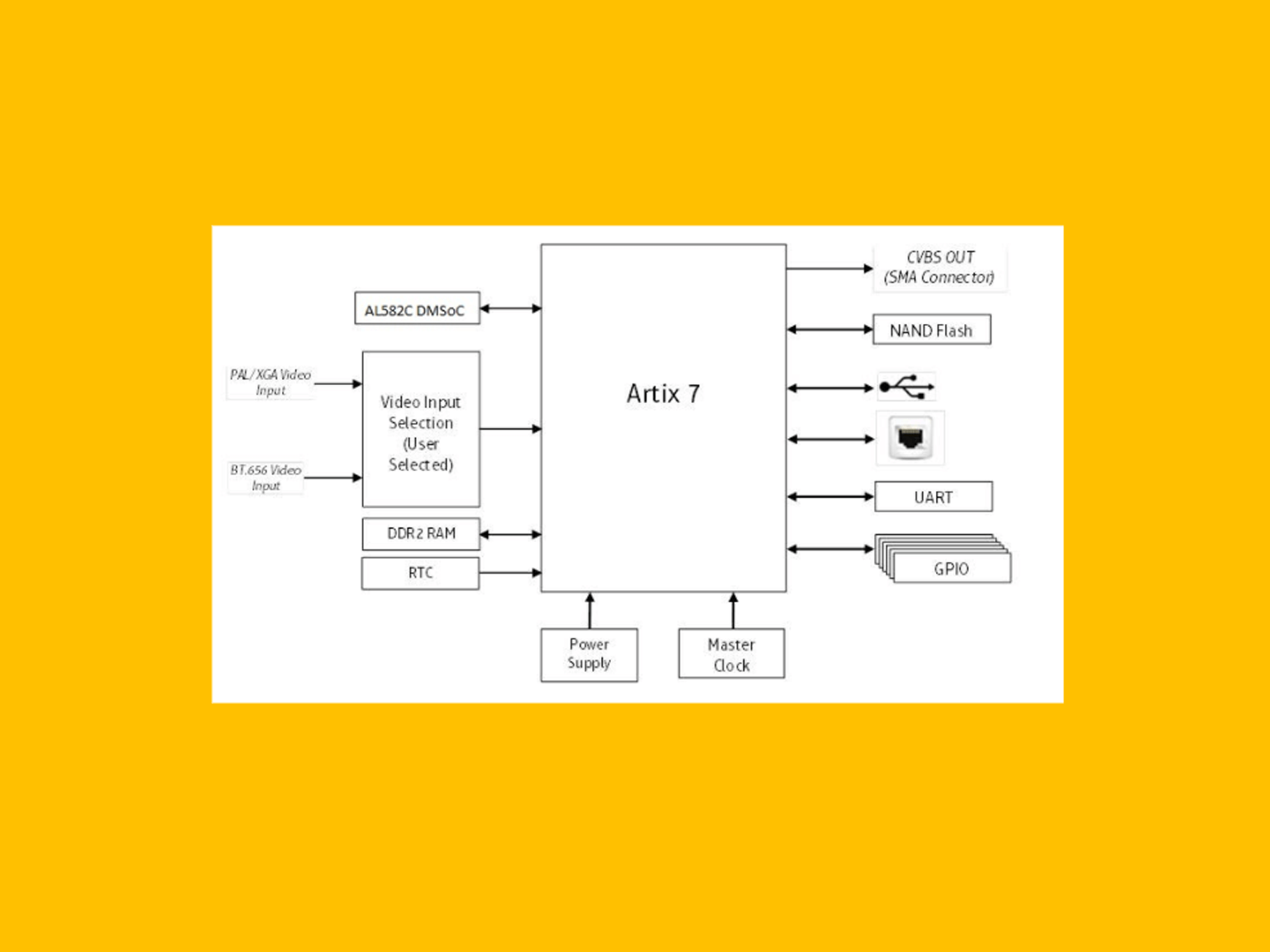

Video Compression and Storage Module

FPGA

Artix 7 FPGA from Xilinx

DMSoC

Digital Media System-on-Chip (DMSoC) from Averlogic

(AL582C) for H.264 video compression

Ethernet

10/100 Mbps.

Memory

32 GB NAND Flash for video and snapshot storage/

retrieval

1 Gb DDR2 RAM

Video capturing

PaI-B/XGA (monochrome and colour)

Digital video BT.656 standard

Storage

Video and snapshot storage at full format and frame rate on the onboard NAND Flash storage on user command

Control and Communication

RS232 Serial link

Target Detection and Classification

Module

Sub Modules

Backplane Card (BPC)

Interface Card (IFC)

Target Detection Card (TDC)

Important features

Scalable architecture

Input Voltage: 12V @ 10A with over voltage and reverse

polarity protection

Real time frame grabbing at 25 frames per second over

resolution of 1024 x 1024 pixels

194 – 512 x 512 point FFTs per second

FPGAs:

Artix 7-200T FPGA from Xilinx (5Nos.)

Artix 7-75T FPGA from Xilinx (1 No.)

SoC: Zynq 7020 SoC from Xilinx